《数字电路与逻辑设计C》课赛结合项目总结报告

2020-2021学年第一学期,在科技1803班和科技1804班的《数字电路与逻辑设计C》的正常教学进程以外,开展了课赛结合项目的实践活动,场地安排在2#523实验室进行(由于2#523实验室在17、18周进行数字电路课程设计,课赛结合又改到2#431实验室进行)。参加此次实践活动的学生总人数为70人,2-3人组成一队,共分为25个队。教师在QQ班级群中定期发布任务,学生充分利用课余时间学习verilog HDL编程,并根据任务要求进行电路设计,撰写设计报告,教师在QQ班级群中提供在线指导。线下安排实验室现场实验指导,指导总学时数(含验收、答辩8学时)为32学时。

本次课赛结合的实施过程具体如下:

1. Vivado 2018软件的使用,时长为6学时。因为课前已要求学生安装好Vivado 2018软件,因此这里只对未正确安装好Vivado 2018软件的学生进行指导。课堂上通过PPT投影讲授Vivado工程的建立、电路模块的编写、电路的综合、仿真、实现,以及FPGA器件的编程。将编写的Vivado 2018软件的操作指南分发给学生参考使用。因为在课赛结合开始之前的《数字电路与逻辑设计C》课程中已经讲授过verilog HDL的基础知识,并要求学生课余自主深入学习verilog HDL知识,因此课赛结合中的verilog HDL教学以实例讲解和编程训练为主。此次设计任务要求学生采用verilog HDL编写板载100MHz晶振的分频电路,实现周期为1秒的对称方波的输出。首先要求学生复习计数器的知识,并采用Multisim软件设计和仿真M=60的同步计数器;然后,课堂上提供一段M=60同步计数器的verilog HDL源代码,讲解代码的编写思路,并注意引导学生认识电路硬件编程与普通计算机软件编程的区别。为仿真计数器模块的功能,课堂上提供一段测试代码,给学生分析测试代码的功能和编写方法,并指导学生完整的进行计数器电路的综合和功能仿真过程,观察和理解仿真工作波形,查看综合出的电路原理图。通过PPT投影讲解EGO1开发板的原理图,要求学生自行完成1Hz方波产生模块的工程建立、代码编写、电路综合、功能仿真、布局布线、约束文件编写、器件编程等流程,采用板载LED灯观察秒脉冲的输出效果。

2. LED多路彩灯控制器的设计,时长为6学时。讲授Xilinx FPGA XC7A35T的内部结构,使学生理解基于RAM查找表结构的编程易失性的特点,指导学生将上一次实验中编写的1Hz方波产生电路生成bit文件,下载到板载EEPROM中,实现程序的永久固化。讲授8位LED流水灯的设计思路,指导学生完成8位LED流水灯的程序设计,并可拓展到16位流水灯。在此基础上,要求学生完成LED多路彩灯控制的设计,至少显示两种花型,花型自由定义。

3. 多位数码管的动态扫描显示,时长为6学时。讲授共阴极数码管的工作特点,讲授数码管的静态显示和动态扫描显示的实现方法。引导学生理解EGO1板载8位数码管的段位端共用,公共端独立,因此必须采用动态扫描的方法才能实现多位数码管的数值显示。讲授FPGA通过I/O端口获取按键状态的方法,讲授按键抖动问题的处理办法。指导学生完成两个任务:(1) M=60计数器状态的数码管显示,计数器时钟为1Hz方波;(2)按键编码显示电路的设计,采样按键状态,并在数码管上显示按键编号。

4. 多功能数字电子钟的设计,时长为6学时。任务要求如下:

(1) 利用分频方法实现周期为1s的定时脉冲;

(2) 完成基本的时、分、秒的计时,通过数码管显示当前的时间;

(3) 可以通过按键设置当前的时间;

(4) 具备闹钟功能,可以独立设置3个闹钟,可以查看和修改闹钟时间,为每个

闹钟设置独立使能开关,具备定点声光报时功能;

(5) 可以通过开关控制数码管的显示亮度;

(6) 可以通过温度传感器采集环境温度,并在数码管上显示当前的温度值;

要求撰写设计报告,报告内容应包括:

(1) 总体设计方案

(2) 分功能模块电路的设计

(3) 仿真波形图

(4) 实物演示照片

(5) 问题和经验总结

(6) 参考资料汇总

5. 验收和答辩,时长为8学时。验收和答辩环节邀请电路和电子技术基础教学部的朱旭花、赵林森、王静等老师参加,现场考察“多功能数字电子钟”任务的完成情况并打分。答辩要求每组选派一名代表上台讲解设计过程并现场回答老师的提问,采取教师点评和组间互评的打分方式,最后按照验收60%,答辩30%,报告10%比例计算最终成绩,最终决出一等奖两名、二等奖两名、三等奖三名。

纵观此次课赛结合项目的实施过程,学生的学习兴趣较高,教学秩序良好,实践效果理想。以往在《数字电路与逻辑设计C》的教学过程中,学生虽然学习了数字电路的基础知识,但实际应用能力普遍较弱,尤其是“可编程逻辑器件”这一部分的教学,教材内容较为陈旧,知识过于理论化、抽象化,学生学习掌握较为困难,学过也只是在头脑中留下一些概念和框架,根本不知道这类器件有什么实际用途,可以怎么用,教师在教学过程中对这个问题也颇感无奈。

通过本次课赛结合项目的申请和实施,拉近了课本与现实的距离,开阔了学生的视野,提高了学生理论联系实际的能力。学生普遍反映从本质上真正地理解了“可编程逻辑器件”这个概念,掌握了verilog HDL的基本语法和编程风格,能够运用verilog HDL设计简单的数字电子系统,积累了一定的FPGA设计经验,提高了工程设计能力,为以后参加大学生电子设计竞赛、以及在电子技术领域就业建立了良好基础。

实验室现场指导时的照片:

学生答辩时的照片:

实验室现场指导时的签到表:

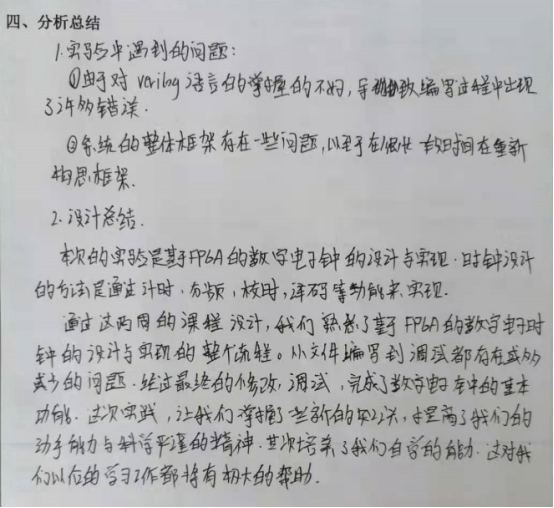

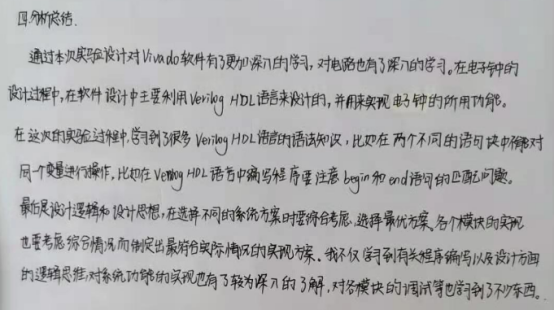

学生的分析总结:

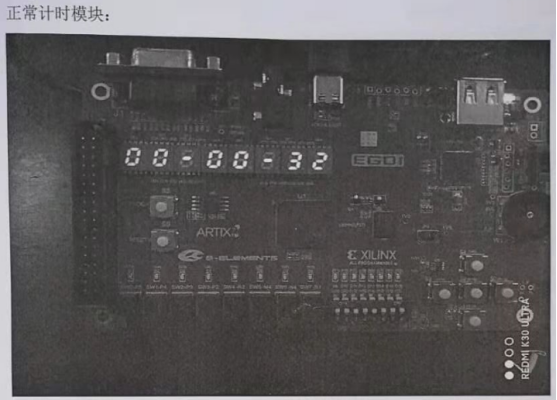

学生的设计作品:

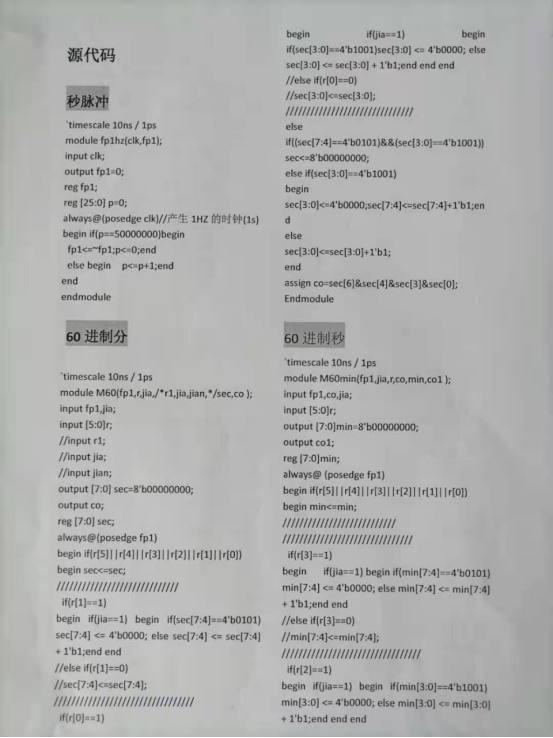

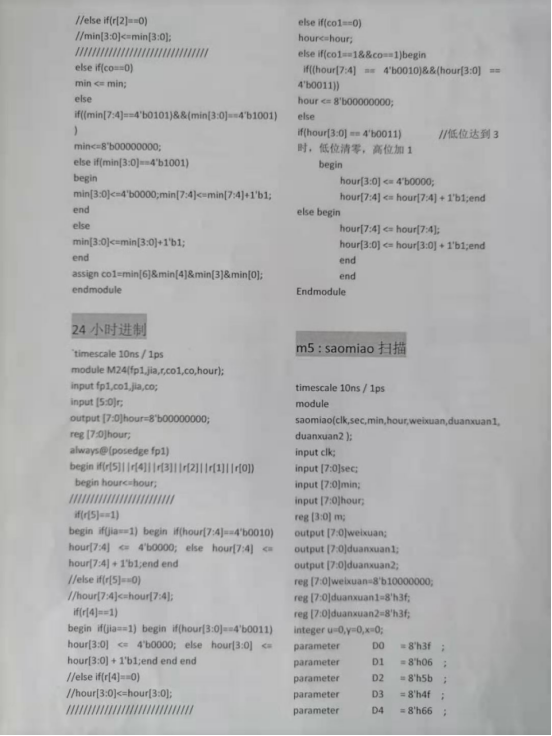

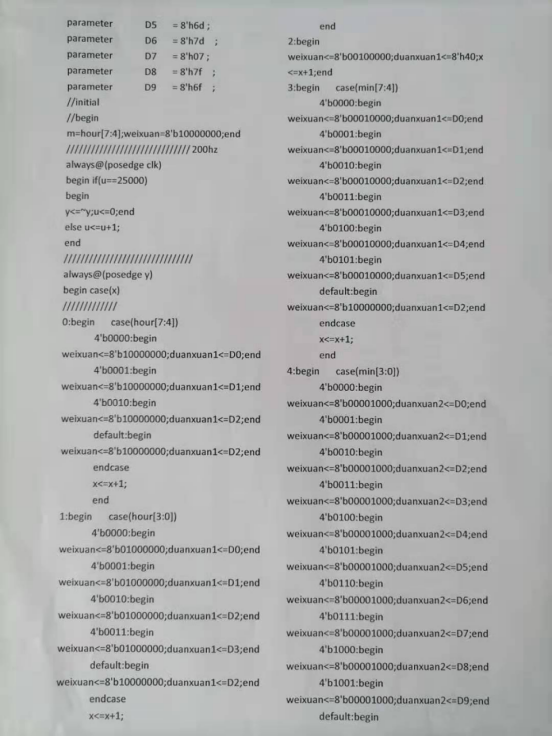

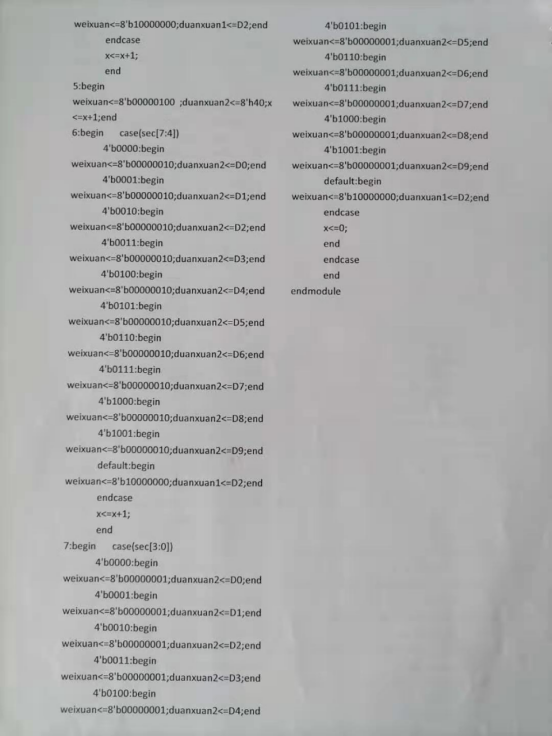

学生编写的代码:

bat365在线登录入口

电路与电子技术基础教学部

陈东

2021年1月8日